1> 文件名命名,小些单词为主且从命名中可以大致读出其功能,例如:fpga_power.v,can_ctrl.v等命名。

2> 顶层top文件的输入输出IO信号使用大些表示,且加上”i/o”标识符表示是输入信号还是输出信号。

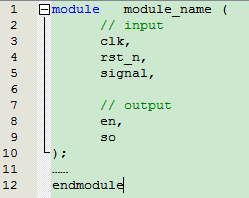

3> 每个模块的书写,模块定义时书写参考如下形式。

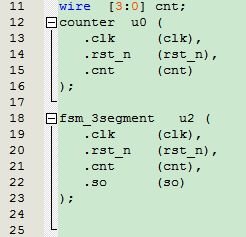

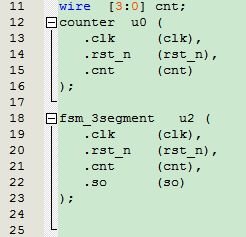

4> 模块例化时的写法,可参考如下。

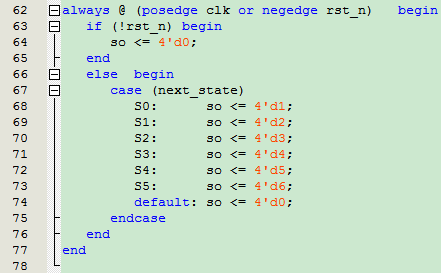

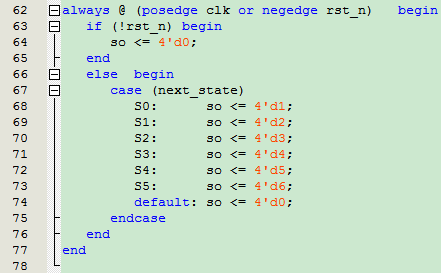

5> always程序块内begin…end要写全。always模块的编写范例如下。

6> 位宽不要浪费,位宽进制都应写清楚,比如8’hFF。

本文共 291 字,大约阅读时间需要 1 分钟。

1> 文件名命名,小些单词为主且从命名中可以大致读出其功能,例如:fpga_power.v,can_ctrl.v等命名。

2> 顶层top文件的输入输出IO信号使用大些表示,且加上”i/o”标识符表示是输入信号还是输出信号。

3> 每个模块的书写,模块定义时书写参考如下形式。

4> 模块例化时的写法,可参考如下。

5> always程序块内begin…end要写全。always模块的编写范例如下。

6> 位宽不要浪费,位宽进制都应写清楚,比如8’hFF。

转载于:https://www.cnblogs.com/airbird/p/verilog_code_style.html